Abstract

Optimizing the Performance of Full adder, NAND by the Use of Parameters of Nano Tube Carbon Field Effect Transistor Technology

Full adder and NAND are the most important parts of digital circuits. Therefore, optimizing the these blocks improves the whole output parameters of digital circuits. In this paper controversial full adder and NAND are designed in CNFET technology and then different parameters of CNFET technology are changed to optimize the speed and power consumption of full adder and NAND. The results of simulation by using HSPICE in .9v are presented. The result of simulation shows the best parameters for better performance of these full adder and NAND in CNFET technology.

Author(s): Seyedeh Somayeh Hatefinasab

Abstract | Full-Text | PDF

Share this

Awards Nomination

Google scholar citation report

Citations : 5001

Electronic Journal of Biology received 5001 citations as per google scholar report

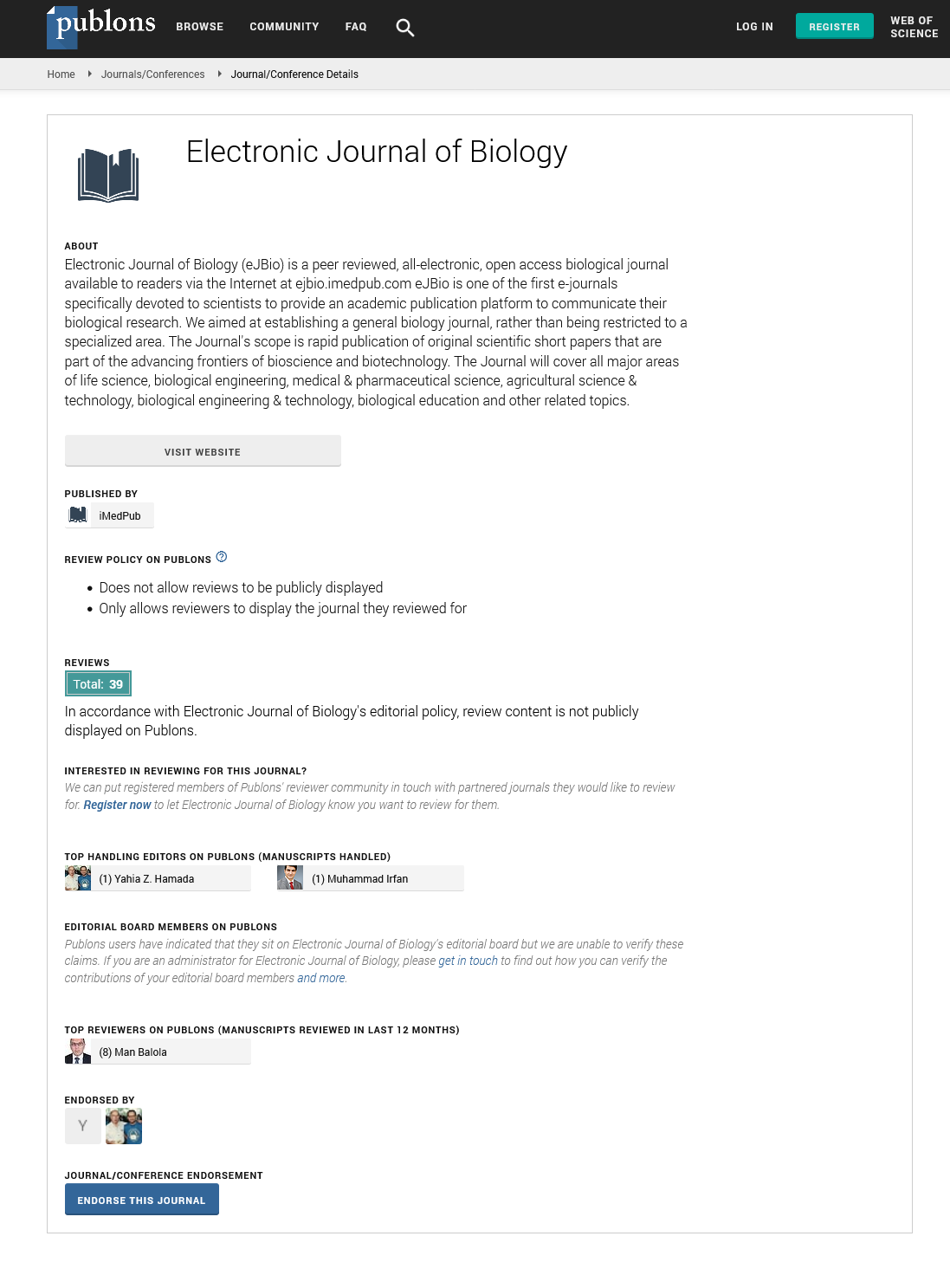

Electronic Journal of Biology peer review process verified at publons

Abstracted/Indexed in

- Google Scholar

- China National Knowledge Infrastructure (CNKI)

- CiteFactor

- Electronic Journals Library

- Zoological Records

- WorldCat

- Proquest Summons

- Publons

- MIAR

- Openaccessarticles.com

- Secret Search Engine Labs

Open Access Journals

- Aquaculture & Veterinary Science

- Chemistry & Chemical Sciences

- Clinical Sciences

- Engineering

- General Science

- Genetics & Molecular Biology

- Health Care & Nursing

- Immunology & Microbiology

- Materials Science

- Mathematics & Physics

- Medical Sciences

- Neurology & Psychiatry

- Oncology & Cancer Science

- Pharmaceutical Sciences